# PX6130KA 1.3MP Product Brief

The PX6130KA is single chip of CIS and ISP. It has excellent noise performance for low light condition and high dynamic range supported by 2-exp line based HDR mode up to 120dB. It has an advanced safety mechanisms of ASIL-B grade for Automotive.

The PX6130KA is single chip of 1.3MP image sensor and ISP for automotive viewing applications. The image sensor delivers high dynamic range up to 120 dB by using dual conversion gain (DCG) method and the ISP enables high quality HDR imaging with advanced image technology. The PX6130KA supports sufficient safety mechanisms of ASIL-B grade.

The HDR image shows no saturation or loss of shadow detail in situations of dramatic contrast such as when entering or exiting tunnels.

The low noise performance enables surround-view and rear view camera, E-mirror applications with excellent image quality.

#### **Applications**

- 360° Surround View Monitoring System (SVM)

- Rear View Camera

- E-Mirror

#### **Product Features**

- ASIL-B safety feature / AEC-Q100

- 120dB HDR with 2-Lane MIPI / DVP Combo output

- YUV / RAW output format

- Low fixed pattern noise of 3.0um BSI Pixel

- Low readout noise

- Programmable frame size, window size, and exposure

- External synchronization support (Genlock)

- One-time programmable memory (OTP)

- AR coating Glass

- Active Dummy Array for offset correction

- Spread Spectrum Clock Generation (SSCG)

- Dead Pixel Correction (DPC)

- Lens Shading Correction (LSC)

- Combine

- Tone Map

- Color Interpolation and Correction

- Denoise

- Dehaze

- Gamma Correction

- Edge Enhancement

- AE/AWB

#### **Technical Specifications**

|   | Parameter             | Typical value                                   |

|---|-----------------------|-------------------------------------------------|

|   | Pixel size            | 3.0 um x 3.0 um                                 |

|   | Effective pixel array | 1336(H) x 1016(V)                               |

|   | Effective image area  | 4.008 mm x 3.048 mm                             |

|   | Optical format        | 1/3.75 inch                                     |

|   | CRA                   | 23.7 °                                          |

|   | AR coating glass      | O (option)                                      |

|   | Input clock frequency | 27 MHz                                          |

|   | Output interface      | 2-Lane MIPI / DVP Combo with<br>RAW / YUV data  |

|   | Max. frame rate       | HDR 30 fps                                      |

|   | Dark signal           | TBD e/sec                                       |

|   | Sensitivity           | TBD V/Lux·s                                     |

|   |                       | HVDD(DVP): 1.7 ~ 1.9V<br>HVDD(MIPI): 1.7 ~ 1.9V |

|   | Power supply          | AVDD: 3.0 V                                     |

|   |                       | DVDD : 1.2 V                                    |

|   | Power consumption     | TBD                                             |

|   | Operating temp.       | -40 ~ 105 °C (Ambient)                          |

|   | Max. dynamic range    | 120 dB                                          |

| İ | SNR                   | TBD dB                                          |

|   | Package type          | A-CSP                                           |

|   | Package size          | 5.950mm x 5.950mm x 0.870mm                     |

|   |                       |                                                 |

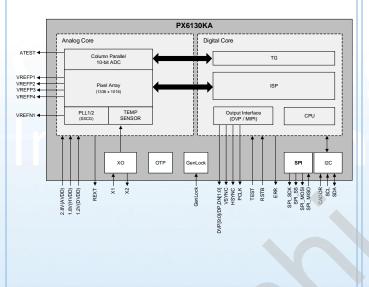

### Functional Block Diagram

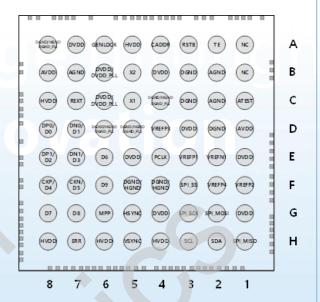

### A-CSP Ball Map

Chip size: 5950 um x 5950 um, 64 ball

### A-CSP Ball Description

| Ball | Ball Name              | 10  | Pull up/<br>Pull down | Ball Description                                                                                                                                                                                                                                                                                                                           |

|------|------------------------|-----|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1   | NC                     | -   | -                     |                                                                                                                                                                                                                                                                                                                                            |

| A2   | TE                     | I   | -                     | Chip test enable                                                                                                                                                                                                                                                                                                                           |

| A3   | RSTB                   |     | -                     | System reset must remain low for at least 8 master clocks after power is stabilized. When the chip is reset, all registers are set to their default values.                                                                                                                                                                                |

| A4   | CADDR                  | I   | -                     | I2C slave device address selection pin. Multi-purpose pin function is supported. When M ulti-purpose pin function mode is enabled, I2C slave device address selection pin is tied t o GND internally. (ERR (Alarm)/UART Rx/PWM3/GPIO[9])                                                                                                   |

| A5   | HVDD                   | Р   | -                     | IO VDD 1.8V DC (MIPI), 1.8V (DVP)<br>It should be tied with nearby HGND by 1uF bypass capacitors.                                                                                                                                                                                                                                          |

| A6   | GENLOCK                | BIO | _                     | External Frame sync input. Slave chip can receive the external frame sync signal from ma ster chip/External Frame sync output. Master chip can output the external frame sync signal through this pad to synchronize all digital outputs of two or more chips. Multi-purpose pin function is supported. (ERR (Alarm)/UART Rx/PWM2/GPIO[8]) |

| A7   | DVDD                   | Р   | -                     | Digital (Core) VDD 1.2V DC<br>It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                                                                                                 |

| A8   | DGND/HGND<br>/DGND_PLL | Р   | -                     | Digital (Core) GND I / O GND<br>PLL GND                                                                                                                                                                                                                                                                                                    |

| B1   | NC                     | -   | -                     | -                                                                                                                                                                                                                                                                                                                                          |

| B2   | AGND                   | Р   | -                     | Analog GND                                                                                                                                                                                                                                                                                                                                 |

| В3   | VSS                    | Р   | -                     | Digital(Core) GND                                                                                                                                                                                                                                                                                                                          |

| B4   | DVDD                   | Р   | -                     | Digital (Core) VDD 1.2V DC<br>It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                                                                                                 |

| Ball | Ball Name              | Ю | Pull up/<br>Pull down | Ball Description                                                                                       |

|------|------------------------|---|-----------------------|--------------------------------------------------------------------------------------------------------|

| B5   | X2                     | 0 | -                     | Master clock input pad (Crystal output)                                                                |

| B6   | DVDD/<br>DVDD_PLL      | Р | -                     | Digital (Core) / PLL VDD 1.2V DC<br>It should be tied with nearby DGND by 1uF bypass capacitors.       |

| В7   | AGND                   | Р | -                     | Analog GND                                                                                             |

| B8   | AVDD                   | Р | -                     | Analog VDD 3.0V<br>It should be tied with nearby AGND by both 1uF bypass capacitors.                   |

| C1   | ATEST                  | О | -                     | Analog test output                                                                                     |

| C2   | AGND                   | Р | -                     | Analog GND                                                                                             |

| СЗ   | DGND                   | Р | -                     | Digital(Core) GND                                                                                      |

| C4   | DGND/HGND<br>/DGND_PLL | Р | -                     | Digital(Core) GND I / O GND<br>PLL GND                                                                 |

| C5   | X1                     | I | -                     | Master clock input pad                                                                                 |

| C6   | DVDD/<br>DVDD_PLL      | Р | -                     | Digital (Core) / PLL VDD 1.2V DC It should be tied with nearby DGND/DGND_PLL by 1uF bypass capacitors. |

| C7   | REXT                   | О | -                     | External Resistor for MIPI                                                                             |

| C8   | HVDD                   | Р |                       | IO VDD 1.8V DC (MIPI), 1.8V (DVP) It should be tied with nearby HGND by 1uF bypass capacitors.         |

| D1   | AVDD                   | P | -                     | Analog VDD 3.0V It should be tied with nearby AGND by both 1uF bypass capacitors.                      |

| D2   | DGND                   | Р | -                     | Digital(Core) GND                                                                                      |

| D3   | DVDD                   | Р | -                     | Digital (Core) VDD 1.2V DC<br>It should be tied with nearby DGND by 1uF bypass capacitors.             |

| D4   | VREFP3                 | 0 | -                     | VREFP3 output.<br>It should be tied with nearby AGND by 1uF bypass capacitors.                         |

| D5   | DGND/HGND<br>/DGND_PLL | Р | -                     | Digital(Core) GND I / O GND<br>PLL GND                                                                 |

| D6   | DGND/HGND<br>/DGND_PLL | Р | -                     | Digital(Core) GND I / O GND<br>PLL GND                                                                 |

| D7   | DNO/D1                 | 0 | -                     | MIPI DN0 Output / Digital Output bit 1                                                                 |

| D8   | DPO/DO                 | 0 | -                     | MIPI DPO Output / Digital Output bit 0                                                                 |

| E1   | DVDD                   | Р |                       | Digital (Core) VDD 1.2V DC<br>It should be tied with nearby DGND by 1uF bypass capacitors.             |

| E2   | VREFN1                 | 0 | -                     | VREFN1 output.<br>It should be tied with nearby AGND by 1uF bypass capacitors.                         |

| E3   | VREFP1                 | 0 | -                     | VREFP1 output.<br>It should be tied with nearby AGND by 1uF bypass capacitors.                         |

| E4   | PCLK                   | 0 | -                     | Digital Output Data can be latched by external devices at the rising or falling edge of PCLK           |

| E5   | DVDD                   | Р | -                     | Digital (Core) VDD 1.2V DC<br>It should be tied with nearby DGND by 1uF bypass capacitors.             |

| E6   | D6                     | 0 | -                     | Digital Output bit 6. Multi-purpose pin function is supported. (ERR (Alarm)/UART Rx/PWM2/GPIO[2])      |

| E7   | DN1/D3                 | 0 | -                     | MIPI DN1 Output / Digital Output bit 3                                                                 |

| E8   | DP1/D2                 | 0 | -                     | MIPI DP1 Output / Digital Output bit 2                                                                 |

| Ball | Ball Name     | Ю   | Pull up/<br>Pull down | Ball Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------|-----|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F1   | VREFP2        | 0   | <u>-</u>              | VREFP2 output. It should be tied with nearby AGND by 1uF bypass capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| F2   | VREFP4        | 0   | -                     | VREFP4 output.<br>It should be tied with nearby AGND by 1uF bypass capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F3   | SPI_SS        | 0   | -                     | Serial Peripheral Interface - Slave Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F4   | DGND/<br>HGND | Р   | -                     | Digital(Core) GND / IO GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F5   | DGND/<br>HGND | Р   | ((-)                  | Digital(Core) GND / IO GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F6   | D9            | 0   | -                     | Digital Output bit 9. Multi-purpose pin function is supported. (ERR (Alarm)/JTAG TMS/UART Tx/PWM1/GPIO[5])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F7   | CKN/D5        | 0   | -                     | MIPI Clock Negative Output / Digital Output bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| F8   | CKP/D4        | 0   | -                     | MIPI Clock Positive Output / Digital Output bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| G1   | DVDD          | Р   | -                     | Digital (Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| G2   | SPI_MOSI      | BIO | - (                   | Serial Peripheral Interface - Master Output, Slave Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| G3   | SPI_SCK       | 0   |                       | Serial Peripheral Interface - Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| G4   | DVDD          | Р   | -                     | Digital(Core) VDD 1.2V DC It should be tied with nearby DGND by 1uF bypass capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| G5   | HSYNC         | O   | -                     | Horizontal synchronization pulse. HSYNC is high (or low) for the horizontal window of interest. It can be programmed to appear or not outside the vertical window of interest. Multi-purpose pin function is supported.  (ERR (Alarm)/JTAG TCK/UART Tx/PWM3/GPIO[7])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| G6   | MPP           | BIO | -                     | Multi-purpose Pin Function Output (Digital Video Out(D11)/ERR (Alarm)/JTAG_TRSTn/UART Tx/PWM1/GPIO[1])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| G7   | D8            | 0   | -                     | Digital Output bit 8. Multi-purpose pin function is supported. (ERR (Alarm)/JTAG TDO/UART Rx/PWM0/GPIO[4])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| G8   | D7            | 0   |                       | Digital Output bit 7. Multi-purpose pin function is supported. (ERR (Alarm)/UART Tx/PWM3/GPIO[3])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| H1   | SPI_MISO      | BIO | -                     | Serial Peripheral Interface - Master Input, Slave Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| H2   | SDA           | BIO |                       | 2-wire serial interface clock, SDA line is pulled up to HVDD by off-chip resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| НЗ   | SCL           | 1   | -                     | 2-wire serial interface data, SCL line is pulled up to HVDD by off-chip resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| H4   | HVDD          | Р   | -                     | IO VDD 1.8V DC (MIPI), 1.8V (DVP) It should be tied with nearby HGND by 1uF bypass capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| H5   | VSYNC         | 0   | -                     | Vertical sync : Indicates the start of a new frame. Multi-purpose pin function is supported to the control of t |

| H6   | HVDD          | Р   | -                     | IO VDD 1.8V DC (MIPI), 1.8V (DVP) It should be tied with nearby HGND by 1uF bypass capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| H7   | ERR           | BIO | -                     | Safety error output. When a safety error occurs, '1' is output. Multi-purpose pin function is supported. (Digital Video Out(D10)/ERR (Alarm)/UART Tx/PWM0/GPIO[0])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Н8   | HVDD          | Р   | -                     | IO VDD 1.8V DC (MIPI), 1.8V (DVP) It should be tied with nearby HGND by 1uF bypass capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |